TSMC, the world’s largest contract chip maker, is preparing to ramp up production using small interchangeable parts called chiplets amid a slowdown in Moore’s Law, the electronics industry's playbook for making smaller, faster and cheaper chips for decades. That was teased out last month when TSMC partnered with Arm to showcase a server chip based on 7-nanometer chiplets.

The proof-of-concept was assembled from smaller separate die like laying out parts on a miniature circuit board. The parts can include CPUs, GPUs, DRAM and various other ICs with prepackaged functions. Each IC can be produced on a different process node to save on cost. To act as though they're on the same die, the chiplets must be linked with a high-speed, high-density and high-bandwidth interconnect in the package.

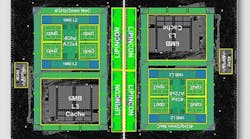

The chip is split into a matching pair of chiplets that each contain Cortex-A72 cores and 6 MB of shared L3 cache. The chips are slapped on a substrate—more commonly called a silicon interposer—with TSMC's Chip-on-Wafer-on-Substrate (CoWoS) technology. The on-die, bi-directional interconnect bus linking the chiplets uses TSMC's LIPINCON technology, which can deliver data rates of up to 8 Gb per pin every second.

Drew Henry, ARM's senior vice president who leads the data center business unit, said in a statement the advanced packaging used in the new chip is the "foundation for production-ready infrastructure SoC solutions." Arm has started selling chip designs dedicated to data centers and cloud servers. It has worked in recent years with Qualcomm, Amazon, Marvell and other customers to roll out server chips produced by TSMC.

TSMC's advanced packaging push is an attempt to chart an alternate path for Moore’s Law, which has slowed after serving as the industry's golden rule for decades, and get around the constraints of what can be crammed inside a single chip. Intel has been pushing hard into packaging after losing the lead in advanced chip production to TSMC, which expects $3 billion in revenue from advanced packaging services in 2019.

Intel has started selling products using its Embedded Multi-die Interconnect Bridge, or EMIB, to connect chiplets on a plane of silicon like puzzle pieces. Intel is also stacking compute and other types of chips on top of each other using its advanced 3D packaging—called Foveros. The company in July introduced what it calls Co-EMIB, which can be used to unite several 3D-stacked Foveros ICs. EMIB acts as the binding agent.

TSMC, the world’s largest made-to-order chip maker with 50% market share, is pushing advanced packaging to its more than 460 customers trying to stand out in areas such as artificial intelligence and data centers. TSMC serves some of the world’s biggest chip designers including Apple, Nvidia and Qualcomm. It has the most advanced process nodes in production, including the 7-nanometer node used in the iPhone 11.

"We believe heterogeneous integration has become a clear trend for many applications," C.C. Wei, TSMC's chief executive officer, said on a conference call with analysts in April. One of the core advantages of chiplets is the ability to build custom chips for the data center and other areas where general-purpose processors are struggling to meet the demands of the IoT and AI. Using chiplets could also help rein in development costs.

Cliff Hou, VP of technology development at TSMC, said in a statement that its CoWoS packaging and LINPINCON interconnect "enable customers to partition large multicore designs into smaller chiplets that deliver better yield and better economics.” Smaller die are less vulnerable to defects, which means more of them can make it through the production process without having to be tossed. That could help prop up profit margins.

TSMC offers other types of advanced packaging. The company has been selling chips based on Integrated Fan-Out (InFO) for use in smartphones and other high-end devices since 2016. More than 20 products with InFO have been shipped or are in development. InFO can be used to connect DRAM to the SoC in a package-on-package (PoP) module, or instead the separate die can be placed side by side in the 2.5D package.

TSMC uses CoWoS technology for what it calls "super-high performance" CPUs, FPGAs and GPUs by cramming more components into the same module. TSMC has started making interposers that measure up to 1,700 mm², or more than double the largest 815 mm² chip it can manufacture. TSMC has also designed a roughly 2,500 mm² interposer that has space for a pair of 600 mm² processors and eight 75 mm² HBM cubes.

TSMC is also working with leading customers on SoIC technology, which opens the door for chips to be stacked on top of each other, in a challenge to Intel's Foveros. TSMC's SoIC technology can be used into connect many disparate die before they are packaged. That enables the stacked chips to be integrated with other SoICs using CoWoS or InFo. The company plans to start manufacturing SoICs in 2021, Wei said.

“Moore's Law is about increasing density,” said Godfrey Cheng, head of global marketing at TSMC, in an August blog post. He pointed to TSMC's advanced packaging as a way to deliver higher density and more performance. He added that “the line is already getting blurry between the definition of a chip and the definition of a system. The line will continue to get more blurry and eventually will be completely eliminated."