The ubiquitous power-rail decoupling capacitor, located as close to its load as possible, has a thankless role and often gets little respect, as compared to the functions of high-performance analog and digital devices. That’s partially because these passive components don’t “add value” to the rail in the conventional functional sense.

Instead, their role is to maintain rail quality despite load-current transients and noise. In many designs, these capacitors are fabricated as discrete devices in the form of multilayer ceramic capacitors (MLCCs).

However, there’s another physical realization of capacitors that offers performance benefits, by using silicon and its fabrication processes. Empower Semiconductor recently introduced the largest silicon capacitor in its ECAP product family for high-frequency decoupling.

Empower Semiconductor's Capacitor Targets Power Integrity

The EC1005P is a single 16.6-μF capacitance device suitable for the most demanding power-integrity targets as often found in high-performance systems-on-chip (SoCs). It’s offered in a compact 3.643- × 3.036-mm, 120-pad chip-scale package (CSP) (Fig. 1). The device comes in a standard 784-µm profile that can be customized for various height requirements.

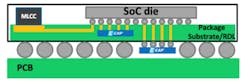

This low-profile device features ultra-low impedance up to 1 GHz and can be embedded into the substrate or interposer of any SoC (Fig. 2). Thus, it’s well-suited for high-performance computing (HPC) and artificial-intelligence (AI) applications.

When it comes to decoupling capacitors, the component and interconnect parasitics can quickly degrade their system-level performance. The EC1005P has an ultra-low equivalent series inductance (ESL) that’s below 1 picohenries (pH, not the chemistry “pH”) and equivalent series resistance (ESR) below 3 mΩ.

Filling the Decoupling Gap

Empower maintains that the silicon-capacitor technology fulfills the “last inch” decoupling gap from the voltage regulators to the SoC supply pins. This approach substitutes several discrete components that have much lower performance and larger footprints with a single monolithic device that provides optimal electrical performance and simplifies engineering complexity.

Further, these silicon capacitors deliver high stability overvoltage and overtemperature and aren’t subject to derating or aging like traditional MLCCs. They require no AC or DC bias derating while all other derating requirements are negligible. This eliminates the need to “over specify” capacitance requirements to account for derating.

If you’re not familiar with silicon capacitors, there’s a brief review of the technology along with its key attributes and a comparison with MLCCs here. The EC1005P ECAP is available for sampling now and will be in volume production in Q4 2024.

Read more articles in the TechXchange: Charging Capacitors.